AIR7310-B Product Guide¶

| AIR-T Model | GPU | FPGA | Part Number (with Enclosure) |

|---|---|---|---|

| AIR7310 | NVIDIA Jetson Orin NX 16GB | Xilinx Artix7 200T | AIR7310-B |

Document Overview¶

This document lists the specifications for the AIR7310-B Artificial Intelligence Radio Transceiver ( AIR-T). Specifications are subject to change without notice. For the most recent device specifications, refer to http://docs.deepwavedigital.com.

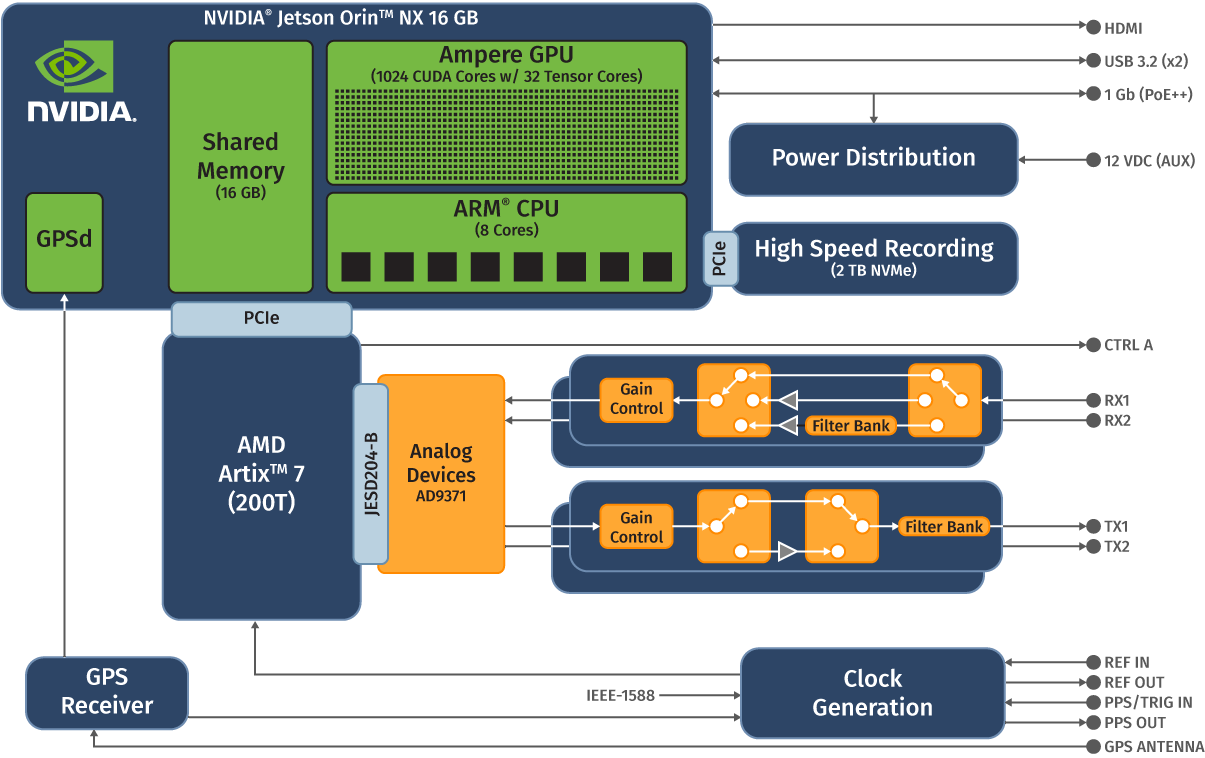

Block Diagram¶

AirStack Software¶

The AIR-T comes pre-loaded with a full software stack, AirStack. AirStack includes all the components necessary to utilize the AIR-T, such as an Ubuntu based operating system, AIR-T specific device drivers, and the FPGA firmware. The operating system is based off of NVIDIA JetPack SDK and is upgraded regularly. Please check for the latest software at www.deepwavedigital.com.

For a full description of the AirStack interface, see our documentation page here.

Mechanical Drawing¶

We provide a PDF file with the mechanical dimensions of the AIR-T enclosure below.

Processors¶

The AIR-T enables software defined radio for any signal processing application by utilizing three classes of tightly coupled processors:

- GPU for highly parallel processing and machine learning

- FPGA for strict real-time operations

- CPU for control, I/O, DSP, and software applications

General Purpose Processors¶

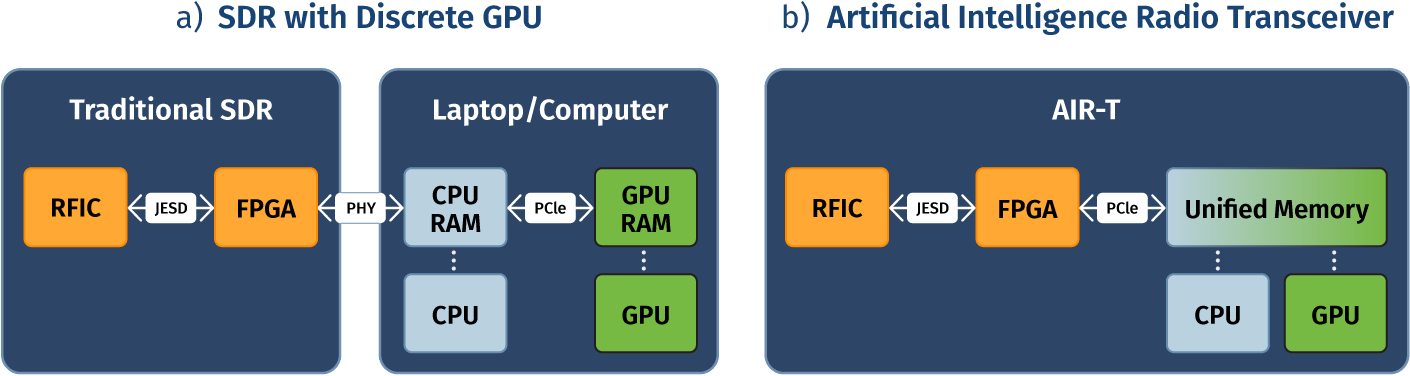

The AIR7310-B Embedded Series AIR-T uses the NVIDIA Jetson Orin NX System On Module (SOM) as its General Purpose Processor (GPP). The Jetson Orin NX SOM contains an ARM Cortex A78AE 64-bit processor (8 cores), an NVIDIA Ampere GPU (1024 cores), and 16 GBytes of memory. The CPUs and GPU all share a common pool of memory, which (along with a unified memory architecture) allows for a zero-copy capability. As illustrated in the figure below, zero-copy eliminates the host-to-device (or device-to-host) memory transfer that is required by SDRs with discrete GPUs, such as an SDR connected to an external laptop or computer. Because of this, an SDR with a discrete GPU will have increased latency that is prohibitive for many applications. By utilizing this zero-copy architecture to remove extra data transfers, the AIR-T minimizes latency compared to other SDR architectures.

For additional details on the NVIDIA Jetson Orin NX please see the module datasheet URL below.

Jetson Modules Technical Specifications

| Parameter | Value |

|---|---|

| Manufacturer | NVIDIA Corporation |

| Model | Jetson Orin NX 16 GB (GPU / CPU) |

| Graphics Processing Unit (GPU) | |

| NVIDIA Ampere GPU |

| 1024 with 32 Tensor Cores |

| 157 TOPS |

| CPU | |

| ARM v8.2 Cortex |

| 2.0 GHz |

| System Memory | 16GB LPDDR5 (102.4GB/s) |

| Storage Capacity | 2 TB NVMe solid state drive |

AMD FPGA¶

The FPGA on the AIR7310-B Embedded Series AIR-T comes pre-loaded with the AirStack firmware to support transmit and receive functionality at various sample rates. Customers may choose to load custom firmware if needed by their application and Deepwave will provide the FPGA interface documentation. The interface documentation includes the pin constraints file and a document that outlines the various interfaces for the FPGA so that customers may develop their own custom IP cores from scratch, i.e., without leveraging any of the AirStack software or driver infrastructure. If customers wish to leverage the AirStack software and driver infrastructure, they are encouraged to purchase a license to the AIR-T FPGA development kit, AirStack Sandbox.

The high-level details regarding the FPGA on the AIR-T are shown below.

| Parameter | AIR7310-B |

|---|---|

| Manufacturer | AMD |

| Family | Artix-7 |

| Model | XC7A200T-2FBG676I |

| LUTs | 215,360 |

| DSP48E1 Slices | 740 |

| Embedded Block RAM | 13.14 kbits |

| Default Time Base | 62.5 MHz or 125 MHz |

| Flash Memory (non-volatile) | 256 Mbit |

External Interfaces¶

Table 4 below describes the external interfaces to the AIR7310-B.

| Interface Label | Location | Connector | Description |

|---|---|---|---|

| Connectors | |||

| Front | HDMI | GPIO for control of external equipment |

| Front | 12 Volt DC power input (2.5mm ID long barrel) | |

| Front | RJ45 | 10/100/1000 BASE-T |

| Front | USB-A | USB 3.0 Super Speed mode (up to 5Gb/s) |

| Front | Micro HDMI | HDMI 2.0 a/b display output (up to 3840 x 2160 at 60Hz) |

| Front | Micro-B USB | Management port for flashing and troubleshooting |

| Front | SMA-F | Transmitter output for channel 1 |

| Front | SMA-F | Receiver input for channel 1 |

| Front | SMA-F | Receiver input for channel 2 |

| Front | SMA-F | Transmitter output for channel 2 |

| Front | SMA-F | 10 MHz frequency source input |

| Front | SMA-F | 10 Mz frequency reference output |

| Front | SMA-F | Input for 1 PPS signal or trigger input |

| Front | SMA-F | Output 1 PPS signal |

| Front | SMA-F | GNSS antenna input |

| Buttons/Switches | |||

| Front | Push Button | Power reset to the unit |

| Back | Toggle Switch | Rocker switch to turn the unit On/Off |

| LEDs | |||

| Front/Back | - | System is powered on |

| Front/Back | - | System has booted to AirStack OS |

| Front/Back | - | PoE++ power is being provided to the system |

| Front/Back | - | Future Use |

| Front | - | Channel 1 transmitter status indicator |

| Front | - | Channel 1 receiver status indicator |

| Front | - | Channel 2 receiver status indicator |

| Front | - | Channel 2 transmitter status indicator |

| Front | - | External frequency reference is selected |

| Front | - | Output frequency reference is provided |

| Front | - | Red=Not Locked, Green=Locked |

| Front | - | Output frequency reference is provided |

| Front | - | Red=Not Locked, Green=Locked |

Transceiver¶

The radio frequency integrated circuit (RFIC) on the AIR-T is the Analog Devices AD9371. This RFIC uses two local oscillators (LO): one for both transmit channels and one for both receive channels. This means that the transmitters and receivers may be tuned to different frequencies at the same time, but both transmit ports will always utilize the same common transmit frequency and both receive ports will always utilize the same common receive frequency.

In addition, the AIR-T Embedded Series contains additional analog circuitry in the two channel receiver chain that improves the noise figure, gain, and filtering.

The Embedded Series AIR-T contains internal clocking circuitry to allow it to operate using an internal clock, have the user provide an external clock, or synchronize to the internal GNSS disciplined oscillator. For the external clock, the products will phase lock to an external 10 MHz reference signal with parameters defined in Table 9. The GPS interface is described in Table 8.

For additional details on the AD9371 please see that datasheet:

| Parameter | Value |

|---|---|

| Manufacturer | Analog Devices |

| Model | AD9371 |

| Frequency Conversion Type | Direct conversion |

Receiver Subsystem¶

The receiver subsystem consists of analog RF circuitry combined with the AD9371 RFIC. Table 6 below highlights the key parameters of the receiver.

| Parameter | Value |

|---|---|

| Number of Channels | 2 (LO shared) |

| Sample Rate | Continuously variable between 7.8125 and 125 MSPS |

| Maximum Bandwidth | 100 MHz |

| Frequency Tuning Range | 300 MHz to 6 GHz |

| Analog Gain | +35 dB |

| Noise Figure | 3 dB |

| Receiver Power Level Control | AGC or manual gain control (between -51.25 and 0 dB) |

| Maximum Input Power | +15 dBm (3dB compression point) +30 dBm (absolute max) |

| ADC Resolution | 14 bits |

| Built-in Calibrations | Quadrature Error Correction, DC offset correction |

A simplified diagram of the analog receiver system into the analog to digital converter (ADC) is shown below. The diagram outlines the gain stages, representing a total gain in the system of +35 dB with 51.25 dB of controllable attenuation. Combining the low noise amplifiers (LNAs) with the variable attenuators (VATTs), the receiver has a total controllable receiver gain range of 69.25 dB.

flowchart LR

%% Define Shapes

RXIN@{ shape: f-circ }

LIM[**Limiter**]

FILT[**Preselector** <br> 8 Bands]

LNA1[**LNA** <br> +18 dB]

VATT1[**VATT** <br> -15 to 0 dB]

subgraph RFIC[**AD9371 RFIC**]

LNA2[**LNA** <br> +17 dB]

VATT2[**VATT** <br> -36.25 to 0 dB]

ADC[**ADC**]

end

%% Define Connections

RXIN -- RX In --> LIM --> FILT --> LNA1 --> VATT1 --> LNA2 --> VATT2 --> ADC

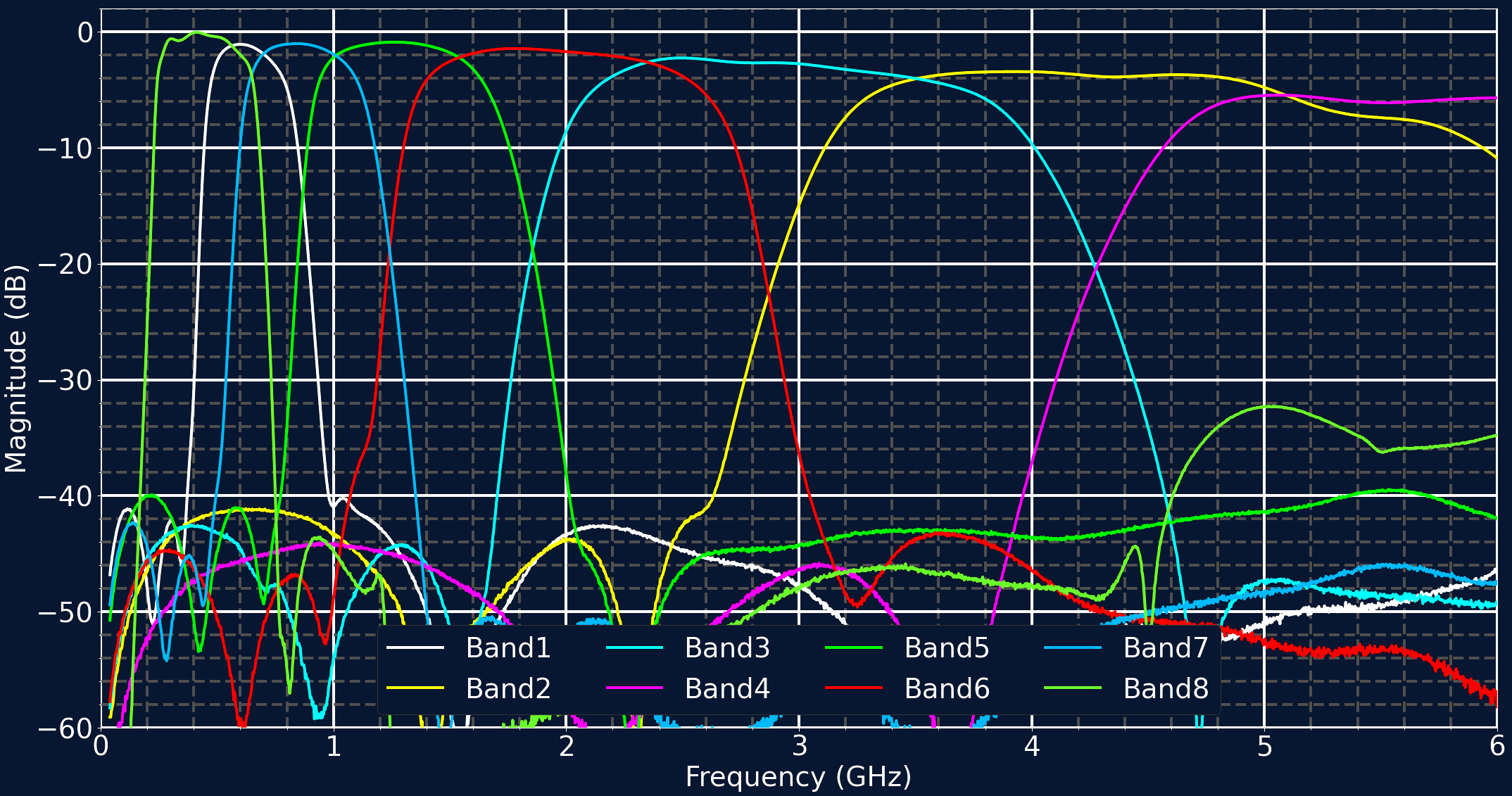

LIM -- Bypass --> VATT1A key feature of the receiver is the ability to filter out interferences with the RF preselector. The preselector consists of 8 bands plus a preselector bypass (not shown). The figure below illustrates the insertion loss of each band.

During operation, the AirStack software will automatically determine the optimal settings for the receiver subsystem components. This optimization occurs for both the preselector band and the VATTs. The preselector band is automatically chosen based on the RF tuning frequency requested and the VATT setting is set based upon the requested gain by the user.

The AirStack API defines the gain of the system to be in the range of [-51.25, 0] dB. In this definition, 0 dB represents decibels at full scale (dBFS), i.e., the configuration when both LNAs are operating and both VATTs are set zero attenuation. When the SDR gain is set to a different value, e.g., -10 dB, the AirStack software has been configured to select the optimal values of the VATTs to produce the desired gain.

Transmitter Subsystem¶

The transmitter subsystem consists of analog RF circuitry combined with the AD9371 RFIC digital to analog converter. The table below highlights the key parameters of the transmitter subsystem.

| Parameter | Value |

|---|---|

| Transmit Channels | 2 (LO shared) |

| Sample Rates | Continuously variable between 7.8125 and 125 MSPS |

| Maximum Bandwidth | 100 MHz |

| Frequency Tuning Range | 300 MHz to 6 GHz |

| Maximum Output Power | +20 dBm |

| Transmit Power Level Control | Manual gain control (between 0-45 dB) |

| DAC Resolution | 16 bits |

| Built-in Calibrations | Quadrature Error Correction, LO leakage correction |

A simplified diagram of the analog transmitter system is shown in the figure below. The diagram shows the RFIC, VATTs, power amplifier (PA), and the transmit filter bank. The maximum output power of +20 dBm occurs when both VATTs are set to zero attenuation and the PA engaged. Including the VATTs allows for 56.95 dB of power control with the PA, with the additional option to bypass the PA.

flowchart LR

%% Define Shapes

FPGA[**FPGA**]

subgraph RFIC[**AD9371 RFIC**]

DAC[**DAC**];

MIXER@{ shape: cross-circ}

VATT1[**VATT** <br> -41.95 to 0 dB];

end

VATT2[**VATT** <br> -15 to 0 dB];

PA[**PA** <br> +20 dB];

FILT[**TX Filters** <br> 4 Bands];

TXOUT@{ shape: f-circ };

%% Define Connections

FPGA --> DAC --> MIXER --> VATT1 --> VATT2 --> PA --> FILT -- TX Out --> TXOUT

VATT2 -- Bypass --> FILT;A key feature of the transmitter is the ability to filter out higher frequency harmonics with the RF filters. The filter bank consists of 4 bands (including a bypass). The figure below illustrates the insertion loss of each band.

During operation, the AirStack software will automatically determine the optimal settings for the transmitter subsystem components. This optimization occurs for the AD9371, the VATTs, and the frequency filters. The filter band is automatically chosen based on the RF tuning frequency requested and the VATT settings are based upon the requested gain by the user.

The AirStack API defines the gain of the system to be in the range of [-56.95, 0] dB. In this definition, 0 dB represents a maximum output power of +20 dBm, i.e., the configuration when both VATTs are set to 0 dB of attenuation and the PA is selected. When the SDR transmit gain is set to a different value, e.g., -10 dB, the AirStack software has been configured to select the optimal values of the VATTs and filter for the desired gain and tuning frequency.

Timing and Clock Circuitry¶

The AIR7310-B has a network of timing and frequency reference sources. Fundamentally, the Clock Synthesizer chip derives time and frequency from a 1 pulse per second (PSS) source. If a PPS source is not provided, the Clock Synthesizer will generate an internal reference. The PPS sources available are network timing from the Ethernet input using IEEE-1588, a 1 PPS input from the SMA connector on the front panel, or a PPS provided from the built-in GPS receiver.

The Clock Synthesizer circuit will create a frequency reference based on the PPS signals and the available Frequency Sources. The user may provide an external 10 MHz frequency reference input or the system is able to use the built-in 10 MHz oscillator.

The Clock Synthesizer is responsible for creating the fundamental clock frequencies needed for the SDR to operate. These signals are then sent to a Clock Distribution chip to be distributed to the required circuits within the SDR. In addition, the Clock Distribution circuit has been paired with two low-noise voltage constrolled oscillators at 122.88 MHz and 125 MHz in oder to provide a highly stable, low phase noise clock.

This theory of operation is illustrated in the diagram below.

flowchart LR

%% Define Shapes

subgraph **Time Sources**

direction TB

NETWORK[**Network** <br> IEEE-1588]

EXT_PPS[**External PPS**]

GPS[**GPS Receiver**]

FPGA[**FPGA**]

end;

subgraph **Frequency Sources**

direction TB

EXT_CLK[**External Ref Clk**]

INT_CLK[**Internal Ref Clk**]

end;

subgraph **Clock Synthesis and Distribution**

direction LR

CLK_SYN(**Clock Synthesizer**)

CLK_DIST[**Clock Distribution**]

subgraph **Ultra Low Phase Noise**

direction LR

LTE_OSC[**122.88 MHz** <br> Internal]

MAIN_OSC[**125 MHz** <br> Internal]

end

CLK_OUT@{ shape: f-circ }

end;

%% Define Connections

NETWORK -- PPS --> CLK_SYN

EXT_PPS -- PPS --> CLK_SYN

FPGA -- PPS --> CLK_SYN

GPS -- PPS --> CLK_SYN

EXT_CLK -- 10 MHz --> CLK_SYN

INT_CLK -- 10 MHz --> CLK_SYN

CLK_SYN == Fundamental Clock ==> CLK_DIST

LTE_OSC --> CLK_DIST

MAIN_OSC --> CLK_DIST

CLK_DIST == Clock Signals ==> CLK_OUTAs mentioned above, the SDR contains internal clocking logic that can leverage an internal reference, a user provided external reference, or the built-in GNSS disciplined oscillator. The following tables describe the parameters for each of these reference sources.

Time Sources¶

As shown in the figure above, the AIR7310-B has the capability to obtaining a time reference (PPS) from both built-in and external sources. The timing source is selected using the AirStack API. The table below provides the specifications for each timing source.

| Network Timing | |

|---|---|

| IEEE-1588v2 |

| RJ-45 |

| < 1us (per specification) |

| External PPS | |

| Front Panel SMA Connector |

| 3.3 Volt LVCMOS 5 Volt Tollerant 50 Ohm Terminated |

| GPS Receiver | |

| Front Panel SMA Connector |

| 5 ns to UTC |

| GPS L1C/A, L5, QZSS L1C/A, L5 GAL E1B/C, E5a BDS B1I, B1C, B2a NavIC L5 GLO L1OF SBAS L1C/A: WAAS, EGNOS, MSAS, GAGAN |

| >-167 dBm (acquisition and track) |

| Active CW detection and removal Dual onboard bandpass filters |

| Advanced anti-spoofing algorithms Galileo OSNMA |

| Active (3.3V DC Bias, 2-20mA Typ, active current limit ~70mA) |

Frequency Sources¶

The AIR7310-B will use the time source and a frequency source to synthesize the various clocks required for system operation. There are two options for frequency sources: Internal and External. The specifications of each of these sources is shown in the table below.

| External Reference Clock | |

|---|---|

| Front Panel SMA Connector |

| 10 MHz |

| +15dBm |

| 50 ohms AC-coupled |

| 3.6 Volts |

| Internal Reference Clock | |

| TCXO |

| ± 0.05 ppm |

| 50 MHz |

For detailed information on interfacing with the GNSS Disciplined Oscillator, see the AIR7310 GNSS Guide.

Clock Synthesis and Distribution¶

The AIR7310-B inputs the time and frequency sources into a clock synthesizer integrated circuit. The clock synthesizer uses these sources to generate the various fundamental clocks necessary for SDR operation. These fundamental frequencies are then sent to a clock distribution integrated circuit for the distribution to the SDR. The table below provides the specifications for both the clock synthesizer and clock distribution chips.

| Clock Synthesizer | |

|---|---|

| Analog Devices AD9545 |

| TCXO |

| ± 0.05 ppm |

| 10 MHz |

| <±180usec @ 1 hour <±4.32msec @ 24 hours |

| Clock Distribution | |

| Texas Instruments LMK04832 |

| VCXO |

| Ultra Low Phase Noise Oscillators | |

| Crystek Corporation |

| VCXO |

| 122.88 MHz and 125 MHz |

| ± 20 ppm |

Power¶

| Parameter | Value |

|---|---|

| Power over Ethernet | PoE++ (60 Watts) |

| Input Voltage Range | 12VDC nominal (11-14 VDCmax) |

| Power Connector | 2.5mm ID long barrel (Switchcraft 761KH) |

Mechanical and Environmental¶

| Parameter | Value |

|---|---|

| Dimensions | 18.65cm × 23cm x 4.35cm (7.34" × 9.06" x 1.71") |

| Operating Temperature Range | 0°C to +50°C non-condensing |

| Weight | 3.3 lbs (1.5 kg) |

Proper Handling¶

The AIR-T Embedded Series is designed for operation in typical indoor conditions with adequate clearance around the unit to support thermal exchange to the surrounding environment.

Standard practices for ESD sensitive equipment should be obsserved during handling and installation.

During the calibration procedure that is run when the radio is initialized, calibration signals may be emitted from both the TX and RX ports. To ensure that connected equipment is not damaged, it is recommended to disconnect the AIR-T from any equipment and terminate with 50 Ohms during the radio initialization.

Warranty¶

Deepwave Digital Inc warrants that the Product will be free from defects in material and workmanship for a period of 12 months from the date of Deepwave Digital's shipment of the Product to the Customer. See the full warranty information here.