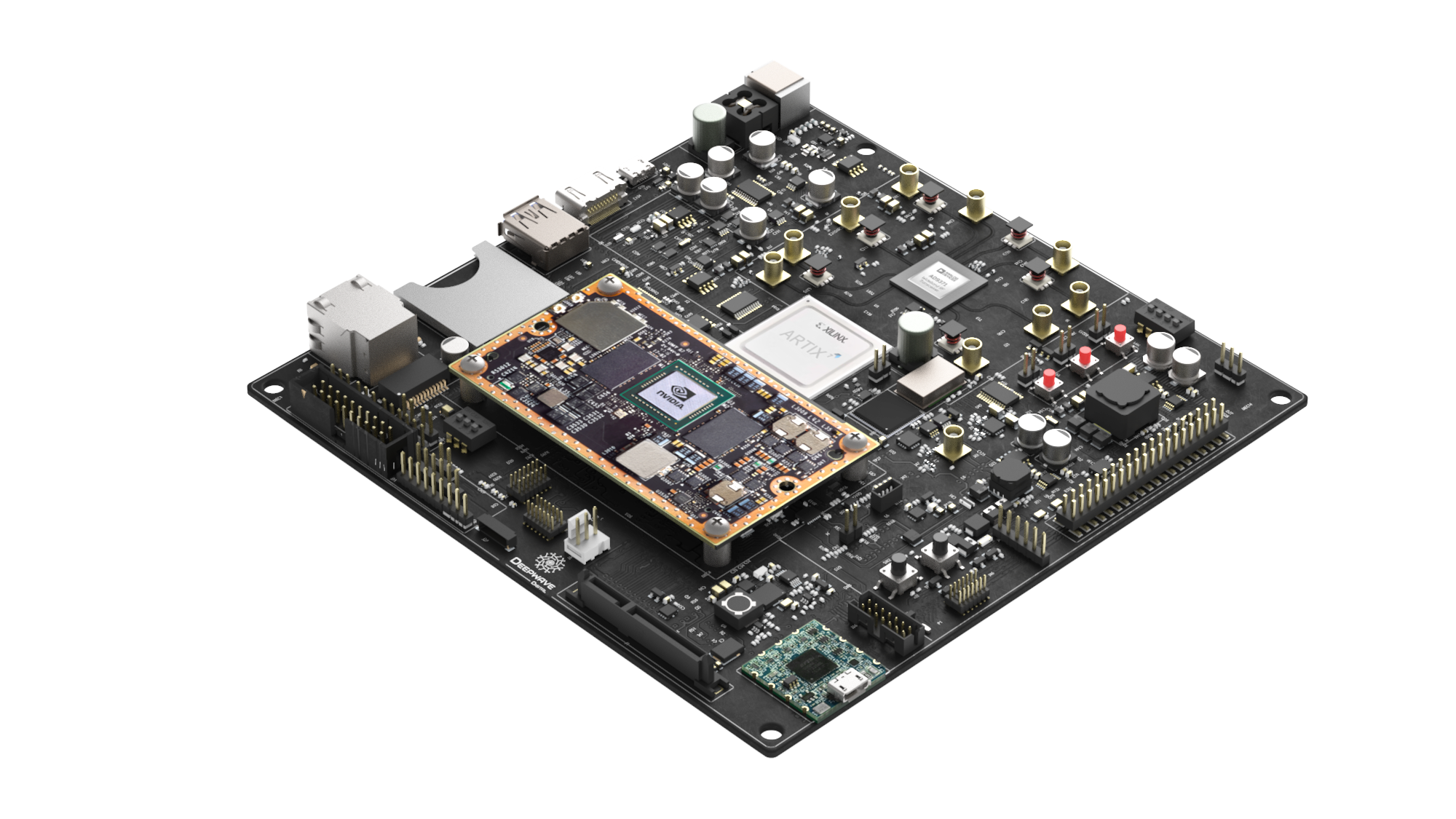

Embedded Series Product Guide¶

| AIR-T Model (Part Number) | NVIDIA GPU Module | AMD FPGA | Enclosure Included |

|---|---|---|---|

| AIR7201-A | NVIDIA Jetson TX2 | AMD Artix7 200T | No |

| AIR7201-B | NVIDIA Jetson TX2 | AMD Artix7 200T | Yes |

Document Overview¶

This document lists the specifications for the AIR7201 Embedded Series Artificial Intelligence Radio Transceiver (AIR-T). Specifications are subject to change without notice. For the most recent device specifications, refer to http://docs.deepwavedigital.com.

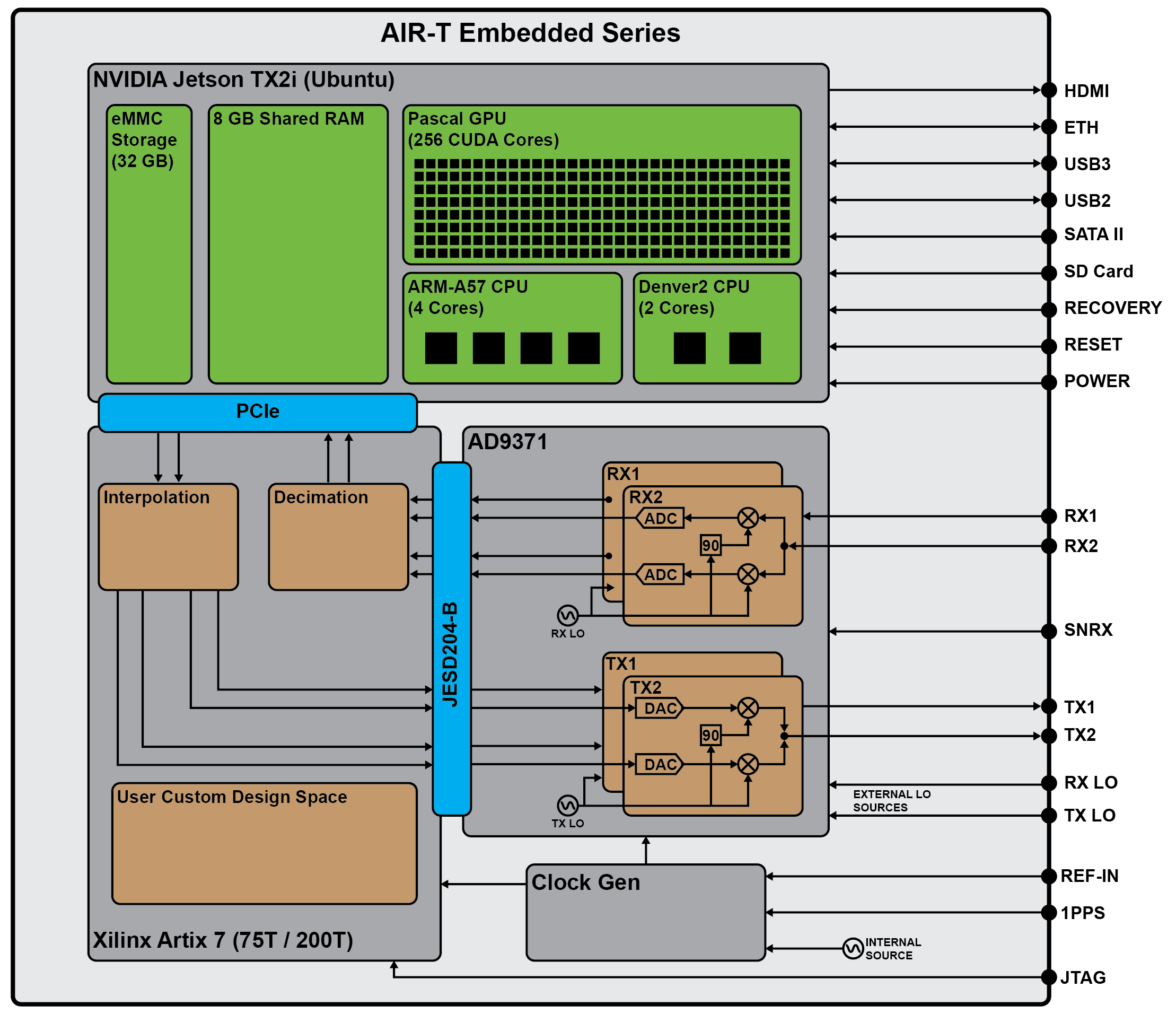

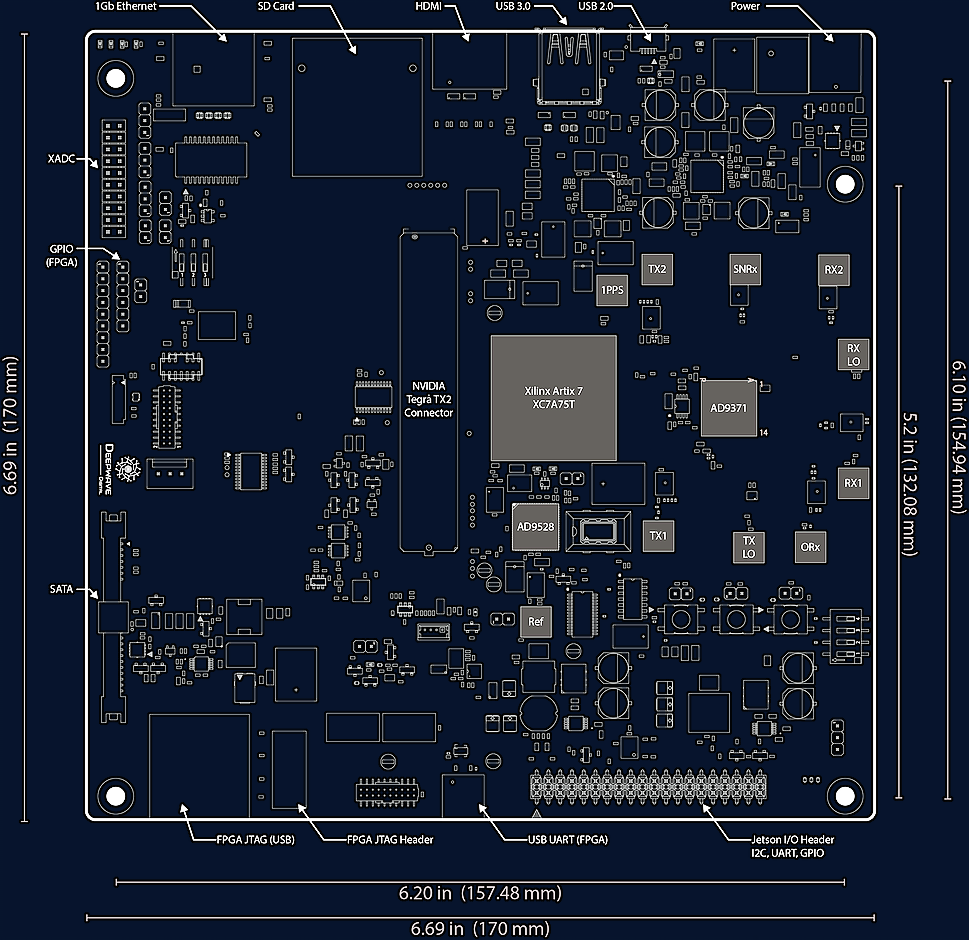

Block Diagram¶

AirStack Software¶

The AIR-T comes pre-loaded with a full software stack, AirStack. AirStack includes all the components necessary to utilize the AIR-T, such as an Ubuntu based operating system, AIR-T specific device drivers, and the FPGA firmware. The operating system is based off of NVIDIA JetPack SDK and is upgraded regularly. Please check for the latest software at www.deepwavedigital.com.

For a full description of the AirStack software guide, see our documentation page here.

AIR7201-B Embedded Series Enclosure¶

The AIR-T may be purchased with or without an enclosure. This documentation applies to both configurations.

Mechanical Drawing¶

We provide a pdf file with the mechanical dimensions of the AIR-T enclosure below.

Processors¶

The Embedded Series AIR-T enables software defined radio for any signal processing application by utilizing three classes of tightly coupled processors:

- FPGA for strict real-time operations

- GPU for highly parallel processing and machine learning

- CPU for control, I/O, DSP, and software applications

General Purpose Processors¶

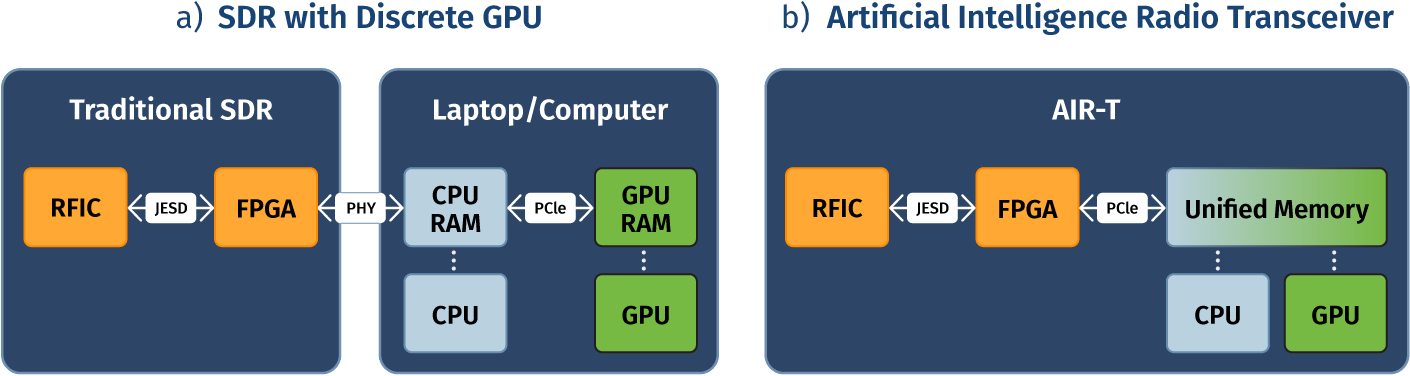

The AIR-T uses the NVIDIA Jetson TX2 System On Module (SOM) as its General Purpose Processor (GPP). The Jetson TX2 SOM contains two ARM processors (6 cores total), an NVIDIA Pascal GPU (256 cores), and 8 GBytes of memory. The CPUs and GPU all share a common pool of memory, which (along with a unified memory architecture) allows for a zero-copy capability. As illustrated in the figure below, zero-copy eliminates the host-to-device (or device-to-host) memory transfer that is required by SDRs with discrete GPUs, such as an SDR connected to an external laptop or computer. Because of this, an SDR with a discrete GPU will have increased latency that is prohibitive for many applications. By utilizing this zero-copy architecture to remove extra data transfers, the AIR-T enables a wide range of low-latency SDR applications.

For additional details on the NVIDIA Jetson TX2 please see the module datasheet URL below. Some of the information from that datasheet is reproduced below.

| Parameter | Value |

|---|---|

| Manufacturer | NVIDIA Corporation |

| Model | NVIDIA Jetson TX2 (GPU / CPU) |

| Packaging | System on Module (SOM) |

| GPU Type | NVIDIA Pascal GPU architecture with 256 NVIDIA CUDA cores |

| CPU Type | ARMv8 (64-bit) heterogeneous multi-processing CPU architecture with two CPU clusters (6 processor cores) connected by a coherent interconnect fabric. ARM Cortex -A57 MPCore (Quad-Core) Processor:

|

| Unified Memory (GPU/CPU shared) |

|

| Storage Capacity | 32GB eMMC 5.1 Flash Storage |

Reconfigurable FPGA¶

The FPGA on the Edge Series AIR-T comes pre-loaded with the AirStack firmware to support transmit and receive functionality at continuously variable sample rates. Customers may choose to load custom firmware if needed by their application and Deepwave will provide the FPGA interface documentation. The interface documentation includes the pin constraints file and a document that outlines the various interfaces for the FPGA so that customers may develop their own custom IP cores from scratch, i.e., without leveraging any of the AirStack software or driver infrastructure. If customers wish to leverage the AirStack software and driver infrastructure, they are encouraged to purchase a license to the AIR-T FPGA development kit, AirStack Sandbox.

The high-level details regarding the FPGA on the AIR-T are shown below.

| FPGA Parameter | AIR7201 |

|---|---|

| Manufacturer | Xilinx |

| Family | Artix-7 |

| Model | XC7A200T-2FBG676C |

| LUTs | 215,360 |

| DSP48E1 Slices | 740 |

| Embedded Block RAM | 13.14 kbits |

| Default Time Base | 62.5 MHz or 125 MHz |

| Flash Memory (non-volatile) | 256 Mbit |

Networking¶

| Interface | Description |

|---|---|

| Ethernet | 10/100/1000 BASE-T, RJ-45 connector |

| WLAN | IEEE 802.11a/b/g/n/ac dual-band 2x2 MIMO (Maximum transfer rate 866.7Mbps) |

| Bluetooth | Version 4.1 |

External Display¶

| Interface | Description |

|---|---|

| HDMI 2.0 a/b | Up to 3840 x 2160 at 60Hz (4k) |

Peripheral Interfaces¶

NVIDIA Jetson TX2¶

| Interface | Description |

|---|---|

| SATA | Version 3.1 |

| SD Card | SD 3.0 or SD-XC cards up to 2 TB |

| USB | USB 3.0 Super Speed mode (up to 5Gb/s) |

| USB 2.0 | High Speed mode (up to 480Mb/s), USB On-The-Go |

| UART | See NVIDIA Jetson TX2 datasheet for information |

| GPIO | See NVIDIA Jetson TX2 datasheet for information |

| SPI | See NVIDIA Jetson TX2 datasheet for information |

| I2C | See NVIDIA Jetson TX2 datasheet for information |

| Audio | I2S or Digital. See NVIDIA Jetson TX2 datasheet for information |

AMD FPGA¶

| Interface | Description |

|---|---|

| JTAG | Programmable via JTAG or Digilent USB to JTAG converter |

| XADC | Integrated Analog with Digital Customization for the FPGA |

| Digital I/O | GPIO, SPI |

| UART | USB to UART bridge |

Analog Devices 9371¶

| Interface | Description |

|---|---|

| GPIO | System monitoring and external attenuator control |

Transceiver Specifications¶

The Radio Frequency Integrated Circuit (RFIC) on the AIR-T is the Analog Devices AD9371. This RFIC uses two local oscillators (LO): one for both transmit channels and one for both receive channels. This means that the transmitters and receivers may be tuned to different frequencies at the same time, but both transmit ports will always utilize the same common transmit frequency and both receive ports will always utilize the same common receive frequency.

In addition, the Embedded Series AIR-T contains internal clocking circuitry to allow it to operate either with an internally-generated clock or by phase locking to an external clock signal provided by the user. When an external clock is selected, the clock signal provided must be a 10 MHz reference signal with parameters defined in Table 13.

The user may also choose to provide an external local oscillator for the transmitter or the receiver. This may be useful in beamforming or direction finding applications. The specifications for the external LO are found in Table 14. Additionally, the functionality may be enabled by following the instructions in Using an External LO.

For additional details on the AD9371 please see that datasheet:

| Parameter | Value |

|---|---|

| Manufacturer | Analog Devices |

| Model | AD9371 |

| Frequency Conversion Type | Direct conversion |

| Parameter | AIR7201 |

|---|---|

| Channels (Shared LO) | 2 |

| Sample Rates | 3.906250 - 125 MSPS Continuously variable |

| Maximum Bandwidth | 100 MHz |

| Frequency Tuning Range | 300 MHz to 6 GHz |

| Gain | +17 dB |

| Tunable Attenuation | 30 dB (0.5 dB increments) |

| Power Level Control | Automatic Gain Control, Manual gain control |

| Maximum Input Power | +15 dBm (w/ 30 dB Attenuation or AGC) |

| ADC Resolution | 16 bits |

| Built-in Calibrations | Quadrature Error Correction, DC offset correction |

| Local Oscillator | Internal (built-in) or external |

| Parameter | Value |

|---|---|

| Channels (Shared LO) | 2 |

| Sample Rates | 3.906250 - 125 MSPS Continuously variable |

| Maximum Bandwidth | 100 MHz |

| Frequency Tuning Range | 300 MHz to 6 GHz |

| Maximum Output Power | +6 dBm |

| Tunable Attenuation | 42 dB (0.5 db increments) |

| Power Level Control | Manual gain control |

| DAC Resolution | 14 bits |

| Built-in Calibrations | Quadrature Error Correction, LO leakage correction |

| Local Oscillator | Internal, external |

| Parameter | Value |

|---|---|

| Clock distribution part number | AD9528 |

| Oscillator Type | VCXO |

| Oscillator Model | Crystek Corporation CVHD-950-125M |

| Oscillator Frequency | 125 MHz |

| Frequency Pull Range | ± 20 ppm |

| Parameter | AIR7201-A | AIR7201-B |

|---|---|---|

| Connector Type | MCX | SMA |

| Input Frequency | 10 MHz | 10 MHz |

| Input Voltage Rating | 3.3V CMOS | 3.3V CMOS |

| Abs Maximum Voltage (50 Ohm) | 3.45 Volts | 3.45 Volts |

| Parameter | Value |

|---|---|

| LO Frequency | 300 MHz to 4 GHz (600 MHz to 800 GHz input frequency) |

| Input Frequency | 2x the desired LO frequency (e.g., 2 GHz input produces 1 GHz LO) |

| Signal Input Power | 0 to +6 dBm |

Additional information: Using an External LO

Note: All AIR-T models perform automatic calibrations when the radio starts and periodically during operation. These calibrations are outlined in Tables 10 and 11. When the radio is initialized, calibration signals may be emitted from both the TX and RX ports. To ensure that connected equipment is not damaged, it is recommended to disconnect the AIR-T from any equipment and terminate with a resistance of 50 Ohms during the radio initialization.

Power¶

| Parameter | Value |

|---|---|

| Input Voltage Range | 8-15 VDC |

| Typical Standby Power Consumption | 9.3 W |

| Power Connector | Barrel Plug, 2.5mm ID x 5.5mm OD x 11.0mm |

| Recommended Power Supply (included) | 80 W, 12 VDC (MEAN WELL P/N GST90A12-P1M) |

Mechanical¶

| Parameter | AIR7201-A | AIR7201-B |

|---|---|---|

| Form Factor | Mini-ITX | Custom enclosure |

| Dimensions | 170mm × 170mm x 35mm (6.7" × 6.7" x 1.4") | 210mm x 192mm x 75mm (8.3" x 7.6" x 3.0" |

| Weight | 0.35 kg (0.8 lbs) | 1.33 kg (2.9 lbs) |

| Operating Temperature Range | -20°C – +70°C | -20°C – +70°C |

Connectors and Headers¶

The AIR-T contains many interfaces with which to interact. In this document, we provide a description of the currently supported interfaces.

AIR-T Drawing¶

Headers¶

| Label | Header | Description | AirStack Version Support |

|---|---|---|---|

| J1 | SATA | SATA port for Jetson TX2 | 0.1.0+ |

| J2 | RX1 | RF receiver input 1 | 0.1.0+ |

| J3 | RST | Jetson reset button | 0.1.0+ |

| J4 | PWR LED | Power indicator for enclosure LED | 0.1.0+ |

| J5 | Ethernet | 1 Gbps Ethernet RJ45 | 0.1.0+ |

| J6 | PWR | Power button | 0.1.0+ |

| J7 | PPS | Trigger (Input) | 0.3.0 |

| J12 | SD Card | Jetson SD card reader | 0.1.0+ |

| J13 | Jetson Module | 400 pin connector for Jetson | 0.1.0+ |

| J14 | Reserved | Reserved | N/A |

| J15 | Jetson Fan | Jetson fan connector | 0.1.0+ |

| J16 | HDMI | Jetson HDMI connector | 0.1.0+ |

| J17 | TX1 | Transmit channel 1 | 0.3.0+ |

| J18 | TX2 | Transmit channel 2 | 0.3.0+ |

| J19 | USB3 | Jetson USB 3.0 interfaces | 0.1.0+ |

| J20 | USB2 | Jetson USB 2.0 and serial connection | 0.1.0+ |

| J21 | Jetson Expansion | Jetson expansion header. See below | 0.1.0+ |

| J22 | RX External LO | External LO for RF front end | 0.2.0+ |

| J23 | TLO | External LO input for transmitter | 0.2.0+ |

| J24 | SPI Voltage | SPI voltage connector | 0.1.0+ |

| J25 | Power Socket | DC power input | 0.1.0+ |

| J26 | FPGA JTAG | FPGA JTAG interface | 0.1.0+ |

| J28 | RX2 | RF receiver input 2 | 0.1.0+ |

| J29 | FPGA SPI Programming | SPI programming interface for FPGA | 0.1.0+ |

| J30 | FPGA SPI Select | - | N/A |

| J31 | FPGA PMOD | - | 0.1.0+ |

| J32 | FPGA XADC | - | N/A |

| J33 | FPGA XADC Analog Input | - | N/A |

| J34 | FPGA XADC Voltage Select | - | N/A |

| J35 | FPGA XADC VIN | - | N/A |

| J36 | FPGA XADC VREF | - | N/A |

| J37 | XADC AGND | - | N/A |

| J38 | XADC AGND L3 | - | N/A |

| J39 | FPGA TP MGTAVCC | - | N/A |

| J40 | TP Ground | - | N/A |

| J41 | FPGA TP MGTAVTT | - | N/A |

| J42 | TP Ground | - | N/A |

| J43 | FPGA XADC VCCINT | - | N/A |

| J44 | Enclosure Fan | Exhaust fan power | 0.1.0+ |

| J45 | FPGA TP (not jumper) | - | N/A |

| J46 | USB UART | - | 0.1.0+ |

| J47 | REF | 10 MHz reference input | 0.2.0+ |

| J48 | Recovery Button | Jetson force recovery button | 0.1.0+ |

| U23 | Digilent USB JTAG | Programming interface for FPGA | 0.1.0+ |

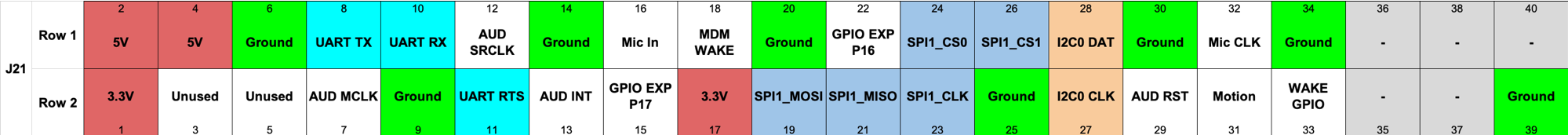

Expansion Header (J21)¶

The expansion header contains many different signals and interfaces to the Jetson TX2 Module. These interfaces are outlined in the diagrams below.

Enclosure Installation¶

In some instances, customers may have purchased the product without an enclosure and desire to install the product in an enclosure purchased by Deepwave Digital. The instructions for installing the product in the aluminum enclosure may be found here.

Proper Handling¶

The AIR7101-A and AIR7201-A are both exposed printed circuit boards with many exposed conductors. It is essential that no conductive material be left near or in contact with the system. Best practices include using an anti-static mat and other ESD procedures when handling sensitive electronic equipment, including low humidity and not exposing the radio to liquids.

Warranty¶

Deepwave Digital Inc warrants that the Product will be free from defects in material and workmanship for a period of 12 months from the date of Deepwave Digital's shipment of the Product to the Customer. See the full warranty information here.